makefile

makefile 的简单示例

假如有三个源文件program.c、pro1.c、pro2.c,program.c文件包含有自定义的头文件lib.h,要求生成可执行文件program。

文件目录结构

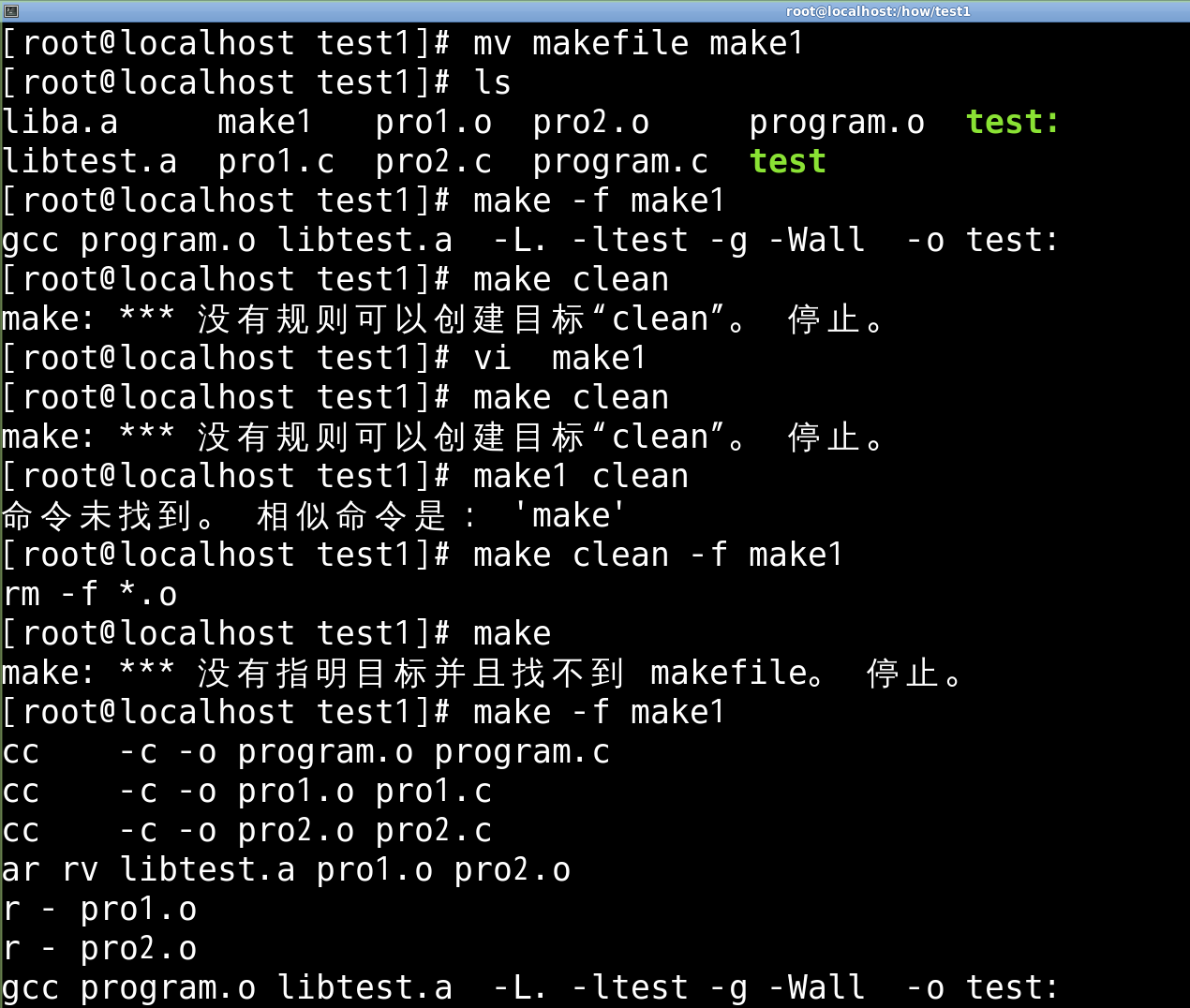

$(opt)=-g -Wall -c test: prgogram.o libtest.a gcc $< -L. -ltest -o $@ libtest.a: pro1.o pro2.o ar rv $@ $^ clean: rm -f *.o ~

出现错误

错误提示

检查makefile 拼写错误

仍然错误

修改关于链接库部分 失败

再探错误原因

$(opt)=-g -Wall -c这句话很明显是错误的修正以后,进行测试

测试结果

最终的makefile如下

1 opt=-g -Wall 2 test: program.o libtest.a 3 gcc $^ -L. -ltest $(opt) -o $@: 4 libtest.a: pro1.o pro2.o 5 ar rv $@ $^ 6 clean: 7 rm -f *.o

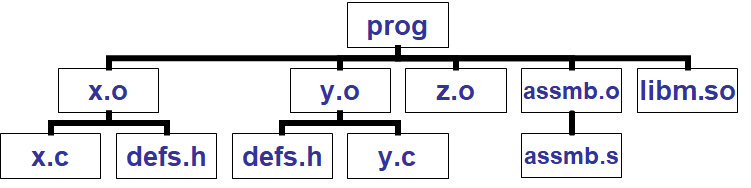

另一个练习题

一个程序包括以下内容。

三个C语言源文件:x.c y.c z.c。 一个头文件defs.h:x.c和y.c都使用了defs.h中的声明。 汇编语言文件:assmb.s 数学运算函数库:/home/mqc/lib/libm.so作下图:

结构依赖图

prog: x.o y.o z.o assmb.o gcc $^ -L/home/mqc/lib/libm.so -lm -o $@x.o: x.c defs.h gcc x.c -cy.o: y.c defs.h gcc y.c -cabssmb: abssmb.s gcc abssmb.s -c

make的基本知识及其变量

基本知识

- make //默认生成第一个目标文件

- make prog1.o //生成指定

- make -f makefile1 //指定读取makefile1

- make clean 注意如果有同名文件 clean 存在,make clean 会出错 以下为解决方案 .PHONY:clean //避免因为clean文件出现,而无法执行删除命令 clean: rm *.o

关于变量

变量的作用

使makefile书写简单

变量的定义

变量的引用

内部变量

1. $@ 2. $^ 3. $<

隐式规则

*.c自动依赖 *.o文件 可以不写出来